Memoria cache a procesorului

Memoria cache a procesorului

| Tip | Cache , memorie de stocare , memorie volatilă |

|---|

| Precedat de | Registrul procesorului |

|---|

| Urmată de | Memorie computer ( in ) |

|---|

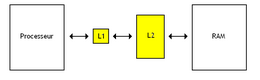

O memorie cache de procesor este o memorie cache hardware utilizată de unitatea centrală de procesare (CPU) a unui computer pentru a reduce costul mediu (timp sau energie) de accesare a datelor din memoria principală . O memorie cache a procesorului este o memorie mai mică și mai rapidă, situată cel mai aproape de o unitate centrală de procesare (sau nucleul microprocesorului ), care stochează copii ale datelor din locații din memoria principală care sunt utilizate frecvent înainte de transmiterea lor în registrele procesorului . Majoritatea procesoarelor au cache-uri independente diferite, inclusiv cache-uri de instrucțiuni și date, unde cache-ul de date este de obicei organizat ca o ierarhie a mai multor niveluri de cache (L1, L2, L3, L4 etc.). Memoriile cache ale procesorului fac parte din memoria principală, la fel ca registrele procesorului și memoria principală, sunt esențiale pentru funcționarea computerului.

Toate procesoarele moderne (rapide), cu câteva excepții, au mai multe niveluri de cache-uri ale procesorului. Primele procesoare care foloseau un cache aveau doar un nivel de cache; spre deosebire de cache-urile de nivel superior ulterioare, acesta nu a fost împărțit în L1d (pentru date) și L1i (pentru instrucțiuni). Aproape toate procesoarele curente cu cache-uri au o cache L1 divizată. De asemenea, au cache-uri L2 și pentru procesoare mai mari, cache-uri L3. Memoria cache L2 nu este de obicei divizată și acționează ca un depozit comun pentru memoria cache L1 deja divizată. Fiecare nucleu al unui microprocesor multi-core are un cache L1 dedicat și de obicei nu este partajat între nuclee. Cache L2 și cache de nivel superior pot fi partajate între nuclee. L4 cache este în prezent limitate și este de obicei găsite pe un fel de memorie dinamică cu acces aleator (DRAM), mai degrabă decât statice cu acces aleator de memorie cu acces aleator (SRAM), pe un circuit integrat mor sau separat microcip ( în mod excepțional, un eDRAM de tip cache poate poate fi utilizat pentru toate nivelurile de cache, până la L1). Din punct de vedere istoric, acesta a fost și cazul cache-ului L1, unde cipurile mai mari au permis integrarea acestuia și, în general, la toate nivelurile de cache, cu excepția poate a ultimului nivel. Fiecare nivel suplimentar de memorie cache este optimizat diferit și tinde să fie mai mare decât cel anterior.

Există alte tipuri de cache, cum ar fi buffer-ul de traducere (TLB), care face parte din unitatea de gestionare a memoriei (MMU) și care este montat pe majoritatea procesorelor.

Note și referințe

- (fr) Acest articol este preluat parțial sau în totalitate din articolul Wikipedia în limba engleză intitulat „ CPU cache ” (a se vedea lista autorilor ) .

- Franck Delattre, „ L'architecture Intel Nehalem ” , pe hardware.fr , BeHardware.fr ,17 septembrie 2008(accesat pe 29 ianuarie 2020 )